- A method for mitigating errors known as Single Event Upsets (SEUs) caused by radiation on programmable sequential electronic circuits;

- An effective technique for mitigating the effects of single event transients (SETs) in combinational circuits using an SET Suppressor;

- A method and circuit structure for suppressing SEUs or glitches in digital electronic circuits; and

- A method and circuit structure for supressing Multiple Bit Upsets in sequential circuits.

Advantages

Advantages

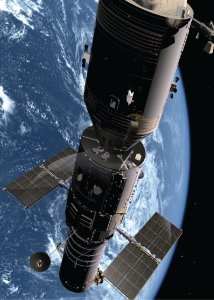

- Digital electronic circuits, such as those used in space aircraft, are subject to interference caused by radiation resulting in errors, known as Single Event Transients (SETs) and Single Event Upsets (SEUs). SETs and SEUs can lead to effects that may or may not permanently damage circuitry. Traditional SEU mitigation solutions rely on duplication or triplication of the circuit and a comparison of the outputs of the duplicate circuits. These solutions take up significant areas on the circuit board and consume large power resources.

- Advanced Circuit Designs do not require duplication or triplication of the circuits but enable better detection and mitigation of errors in Field Programmable Gate Arrays (FPGAs) and ASICs compared to leading solutions available. The power consumption of electronics is significantly reduced and savings of up to 67% of the area on the circuit board can be achieved.

- Application of Advanced Circuit Designs in micro-satellites and other aerospace craft requiring resilience to the effects of radiation;

- Potential partnership with NMMU to progress testing and use of the designs.